北理工團隊在新型二維鐵電研究方面取得重要進展

發布日期:2024-02-26 供稿:物理學院 攝影:物理學院

編輯:王莉蓉 審核:陳珂 閱讀次數:

鐵電材料所展現出的宏觀鐵電性,來源于電偶極矩自發排列形成的集體極化效應。并且,鐵電極化狀態可通過外部電場切換。基于鐵電性的這種優勢,鐵電薄膜廣泛應用于場效應晶體管,非易失性存儲器件和智能傳感器等領域。當傳統鐵電材料如BaTiO3、PbTiO3和BiFeO3厚度減小時,由于退極化場、表面懸掛鍵和界面效應的制約,鐵電性會極大減弱甚至消失。近年來,新興的二維鐵電材料由于界面無懸掛鍵、抗應變性能強、易與其余材料堆疊構建異質結等優勢,受到大家的廣泛關注。二維鐵電材料如CuInP2S6,SnTe,α-In2Se3等相繼被研究和應用。然而,雖然以上二維鐵電材料已經被確定,但具有強鐵電極化狀態和穩定偶極子的二維鐵電材料仍鮮有報道。理論研究發現CuCrX2 (X= S, Se)是一類多鐵材料,二者的反鐵磁性質早已被研究。近期,CuCrS2的面內和面外鐵電性被實驗證實,其鐵電性來源于在CrS2層間Cu原子的偏離位移。其中,CuCrSe2晶體中Cu原子占據相似的配位結構,被認為可實現二維鐵電性質。盡管如此,由于合成超薄二維CuCrSe2納米片仍舊存在挑戰,目前尚無確鑿證據證明CuCrSe2具有鐵電性,對其鐵電性的相關研究也尚未開展。

基于以上研究現狀及存在難題,近日,北京理工大學周家東教授(通訊作者)等通過化學氣相沉積方法合成了厚度可控的二維CuCrSe2納米片。本文通過球差電子顯微鏡研究CuCrSe2的晶體結構,證明Cu原子插層進入到CrSe2層間。通過二次諧波強度隨溫度的變化證明CuCrSe2的居里溫度高達800 K。利用壓電響應力顯微鏡在5.2 nm厚度的CuCrSe2納米片上觀察到了可切換的鐵電極化和明顯的鐵電遲滯回線。此外,在偏壓的施加下,面內和面外鐵電極化可在鐵電器件中進行切換。該研究為構建具有高居里溫度的二維鐵電材料提供了新的策略。文章以“Chemical vapor deposition synthesis of intrinsic high-temperature ferroelectric 2D CuCrSe2”為題發表于期刊Advanced Materials上,北京理工大學博士研究生王平,碩士研究生趙洋和博士后那睿為該論文共同第一作者。

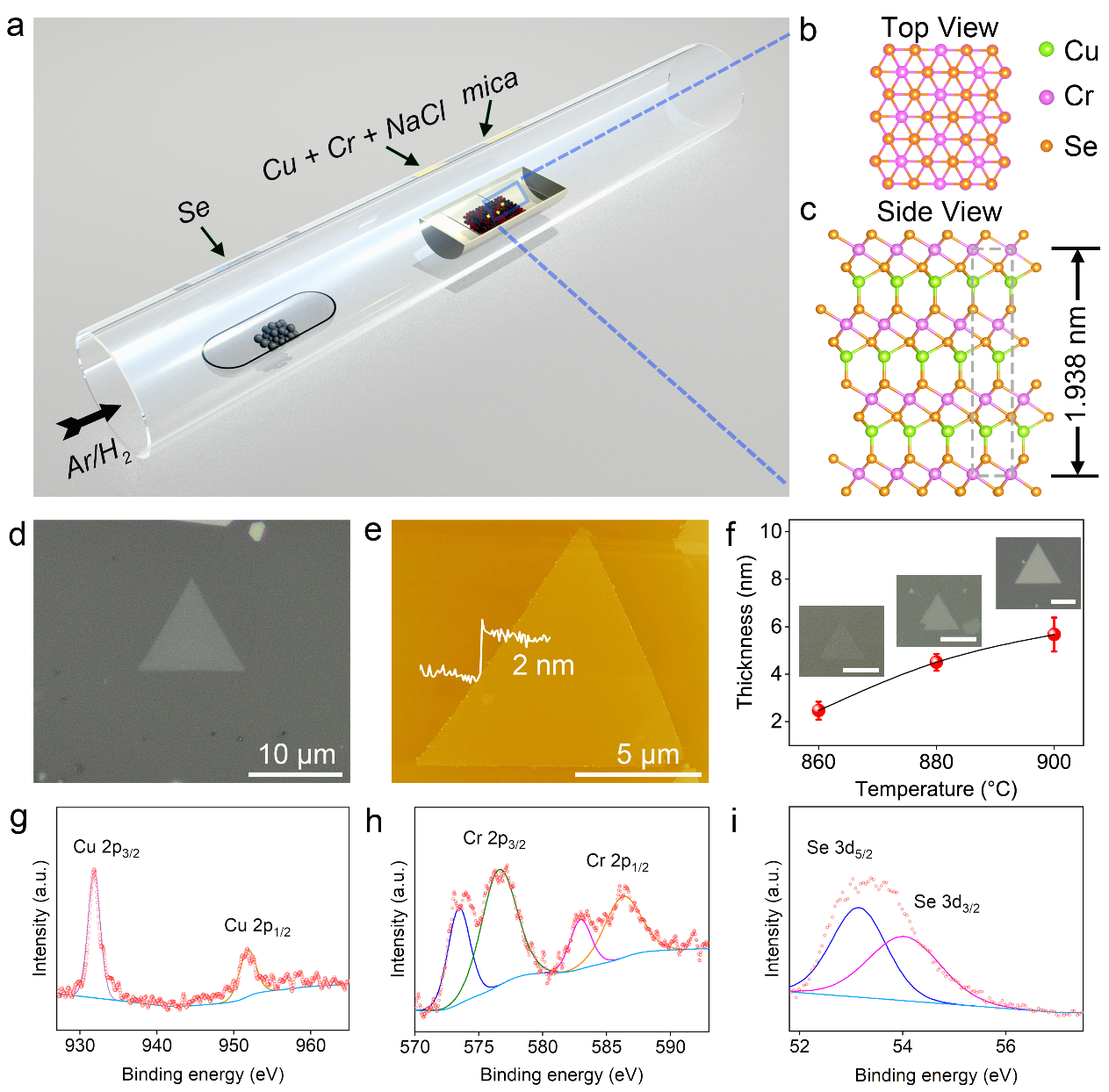

圖1.CuCrSe2納米片的合成及相關表征

本文采用CVD法合成了CuCrSe2納米片,生長過程如圖1a所示。CuCrSe2原子結構如圖1b和1c所示。CuCrSe2晶體屬于R3m空間群,晶格常數a=b=0.36768nm,c=1.938nm。CuCrSe2可認為是準2D晶體結構,其中Cu原子插層進入到以3R順序堆疊的CrSe2層間,并占據四面體配位。Se的反應溫度、Ar氣流速和生長溫度都對CuCrSe2晶體生長存在影響。如圖1f所示,通過對生長溫度進行調控,從而可以調控CuCrSe2納米片的厚度。此外,如圖1g-i所示,利用X射線光電子能譜(XPS)對CuCrSe2納米片中的Cu、Cr和Se元素價態進行研究,各元素價態與之前文獻報道一致。綜上所述,我們合成出高質量的CuCrSe2晶體材料。

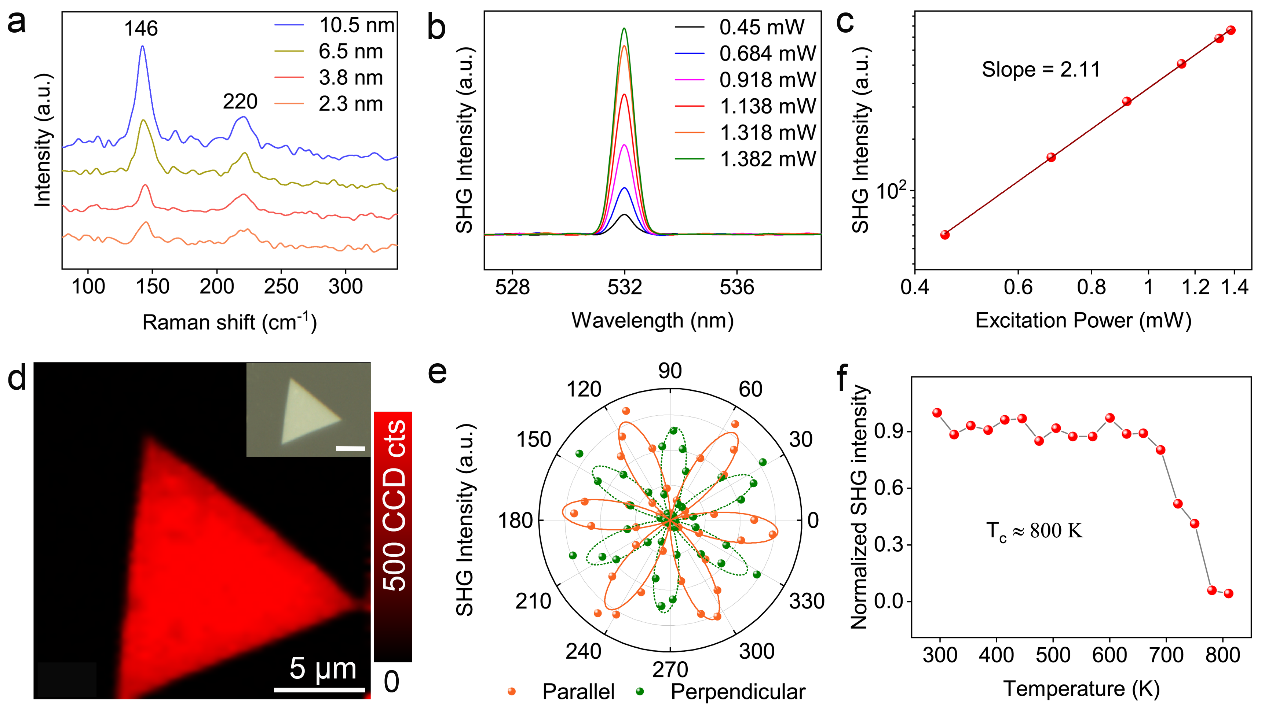

圖2.CuCrSe2納米片的拉曼光譜和SHG表征

圖2a展示了不同厚度的CuCrSe2的拉曼光譜。支撐材料圖S5展示的基于密度泛函理論(DFT)計算的聲子譜和拉曼光譜,與實驗結果相吻合。由于在CuCrSe2晶體中,Cu原子插層進入到CrSe2層間,CuCrSe2晶體具備非中心對稱結構,因此,利用SHG進一步表征CuCrSe2的光學性質和鐵電性質。圖2d給出了CuCrSe2晶體的SHG成像。SHG成像顯現出均勻的形貌,表明所合成CuCrSe2的晶體組成均勻。CuCrSe2晶體中隨溫度變化的SHG強度用于觀測鐵電相變。圖2f給出SHG強度隨溫度變化的歸一化曲線,證明CuCrSe2晶體的居里溫度TC約為~800 K,高于其他已報道的二維鐵電材料。

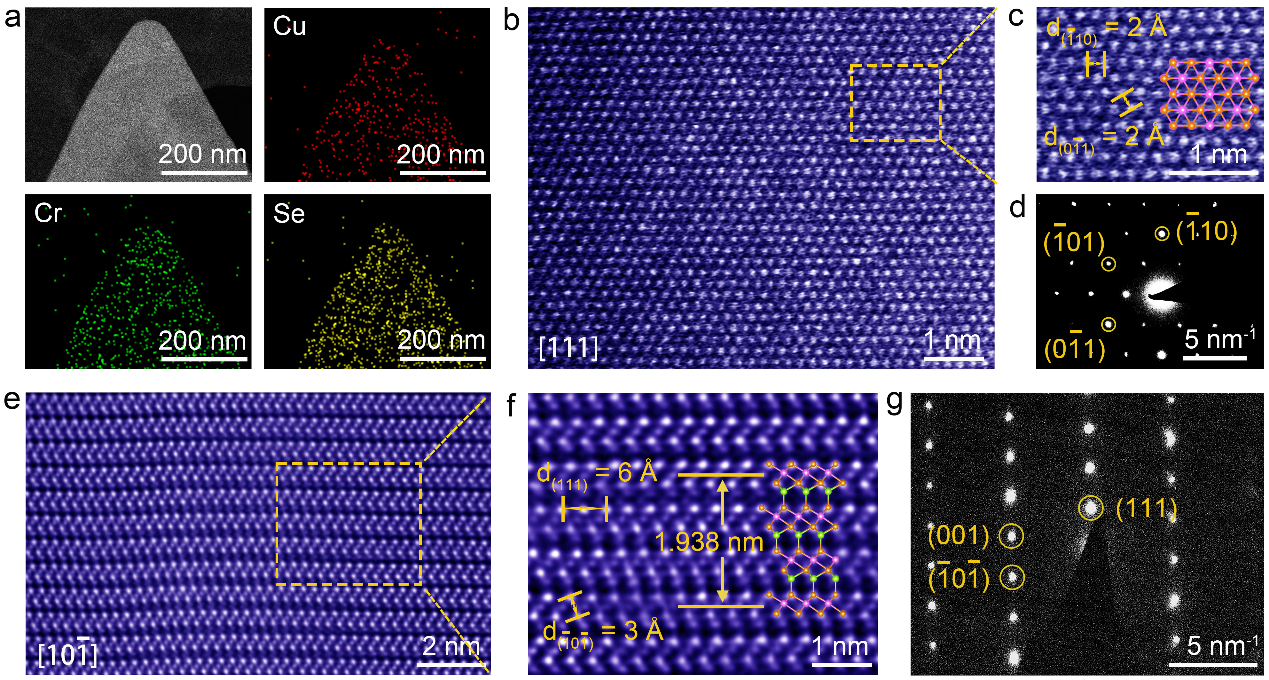

圖3.CuCrSe2納米片的晶體結構表征

利用高分辨球差電子顯微鏡對合成的CuCrSe2樣品晶體結構進行研究。圖3a顯示了超薄CuCrSe2納米片的低分辨射電子顯微鏡圖像,其中能譜(EDS)圖體現出CuCrSe2中Cu、Cr和Se元素均勻分布,證明獲得了高質量CuCrSe2晶體。圖3b給出沿[111]晶軸方向的CuCrSe2納米片平面STEM圖,這與預測的CuCrSe2晶體模型一致。圖3d中CuCrSe2沿[111]軸向對應的SAED花樣證實了所合成樣品為高質量單晶。CuCrSe2納米片沿[10-1]晶軸方向的HAADF-STEM圖如圖3e所示。顯然,Cu原子插層進入到CrSe2層間,與CuCrSe2晶體的模擬截面STEM圖相吻合。此外,對應的SAED花樣(圖3g)與模擬原子結構的傅立葉變換(FFT)花樣(圖S7)相一致,這表明所合成的CuCrSe2的原子結構與理論模型一致。

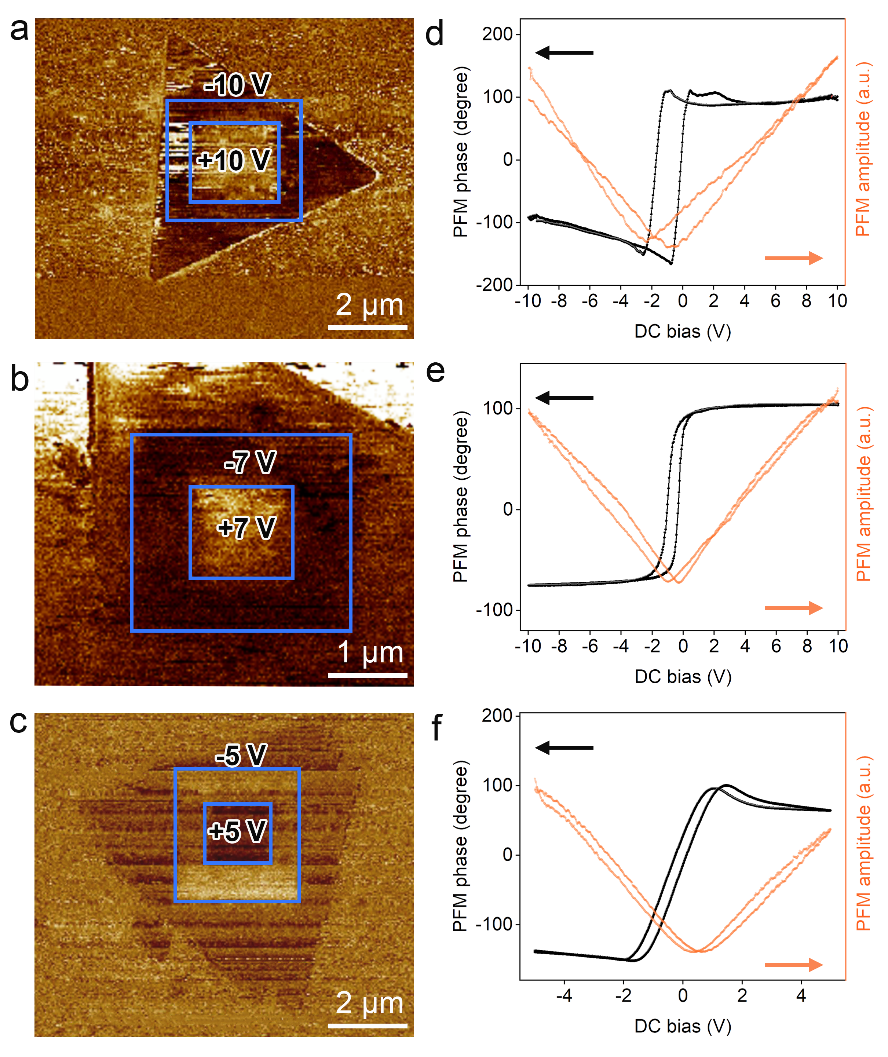

圖4.不同厚度CuCrSe2納米片(32.8 nm,18.2 nm和5.2 nm)中極化反轉

通過壓電響應力顯微鏡(PFM)觀測CuCrSe2納米片中的鐵電性。在厚度為8.7 nm的CuCrSe2納米片中進行PFM“讀寫”操作后,觀察到面內(IP)和面外(OOP)鐵電極化,這在支撐材料進行討論。隨后,對不同厚度的CuCrSe2納米片的本征OOP鐵電性質進行深入研究,結果表明CuCrSe2納米片中存在OOP鐵電性。值得注意的是,在厚度為2.3 nm的CuCrSe2納米片中觀察到壓電響應(圖S10),經過PFM“讀寫”操作后,并沒有觀察到OPP極化。這是由于隨著CuCrSe2納米片厚度的減小,鐵電極化減小所致。

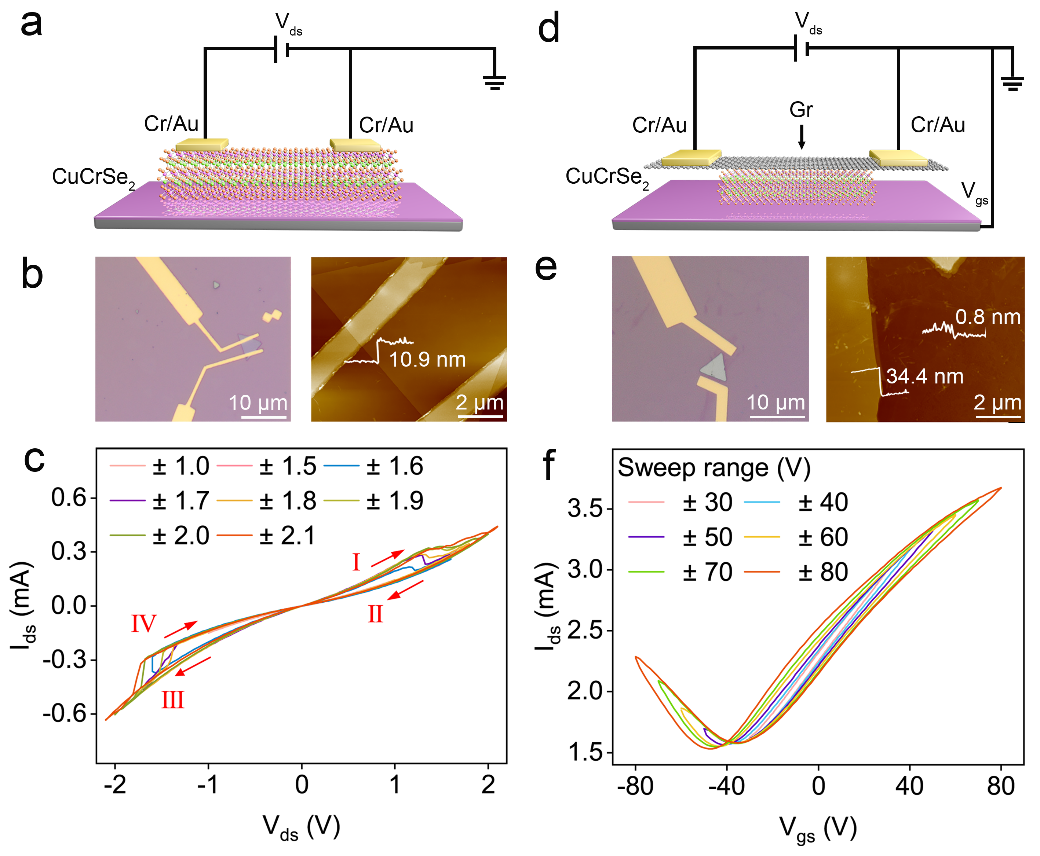

圖5.基于CuCrSe2鐵電器件的電學測量

本文制做了水平和垂直器件,用于驗證CuCrSe2的存儲應用。在不施加柵壓的情況下,水平切換源漏電流,獲得了不同最大掃描電壓下的 Ids-Vds 曲線 (圖5c)。顯然,從1.6V開始, Ids-Vds 曲線出現了遲滯回線,表明在1.6V附近有兩個臨界電壓對應于IP鐵電極化反轉。當施加正電壓從0到2.1V時,器件進入低阻態(LRS),這源于之前負電壓導致的負極化(過程I)。當電壓達到臨界電壓時,負極化狀態轉變為正極化狀態。減小的電流表明器件進入高阻態(HRS)。當電壓從2.1V掃描到0V時,由于正極化平行于外部電場,器件保持在HRS(過程II)。當施加負電壓從0到2.1V時,正極化狀態開始切換到負極化狀態(過程III)。當負電壓降至1.8V時電流減小,表明該器件進入到LRS。該狀態轉變的延遲是由于極化反轉的緩慢過程。隨后,當負電壓從~1.6V降至0V時,器件保持在LRS(過程IV)。高低阻態可根據外加電場的反轉而切換,證明二維CuCrSe2中存在面內鐵電性。隨后,通過石墨烯(Gr)置于頂部用作載流子傳輸通道,與CuCrSe2堆疊制做成Gr/CuCrSe2垂直器件以實現OOP鐵電開關(圖5d)。在垂直器件中,觀察到周期性的 Ids-Vgs 遲滯回線和明顯的Dirac電壓偏移,這是由于CuCrSe2納米片中OOP鐵電極化切換和從CuCrSe2到石墨烯的電荷轉移。綜上所述,外加電場可調控IP和OOP鐵電極化切換。

本文通過CVD法合成厚度可控的CuCrSe2納米片。通過PFM在厚度僅為5.2 nm的CuCrSe2納米片中觀察到鐵電極化反轉。此外,確定了超薄CuCrSe2納米片的居里溫度 TC 為800 K。利用PFM觀察IP和OOP鐵電極化反轉,并通過水平和垂直器件對IP和OOP鐵電性質進行證明。該工作為構建二維插層材料提供了新策略,并為鐵電材料的應用提供了新機遇。

文獻信息:Chemical Vapor Deposition Synthesis of Intrinsic High-temperature Ferroelectric 2D CuCrSe2. (Adv. Mater., 2024, DOI: 10.1002/adma.202400655)

文獻鏈接:https://doi.org/10.1002/adma.202400655

分享到: